Transistorentwicklung: Von Planar zu CFET definiert die 3D-Integration den Halbleiterfortschritt neu

Mehr als ein halbes Jahrhundert lang wuchs die Halbleiterindustrie, indem sie einer einfachen Regel folgte: Transistoren kleiner machen.Verkleinerte Strukturgrößen führten zu höherer Leistung, geringerem Stromverbrauch und geringeren Kosten pro Transistor.Doch heute ist dieser Weg an seine physischen und wirtschaftlichen Grenzen gestoßen.Die Ära der reinen Skalierung ist vorbei und eine neue Ära beginnt strukturelle Innovation und 3D-Integration hat begonnen.

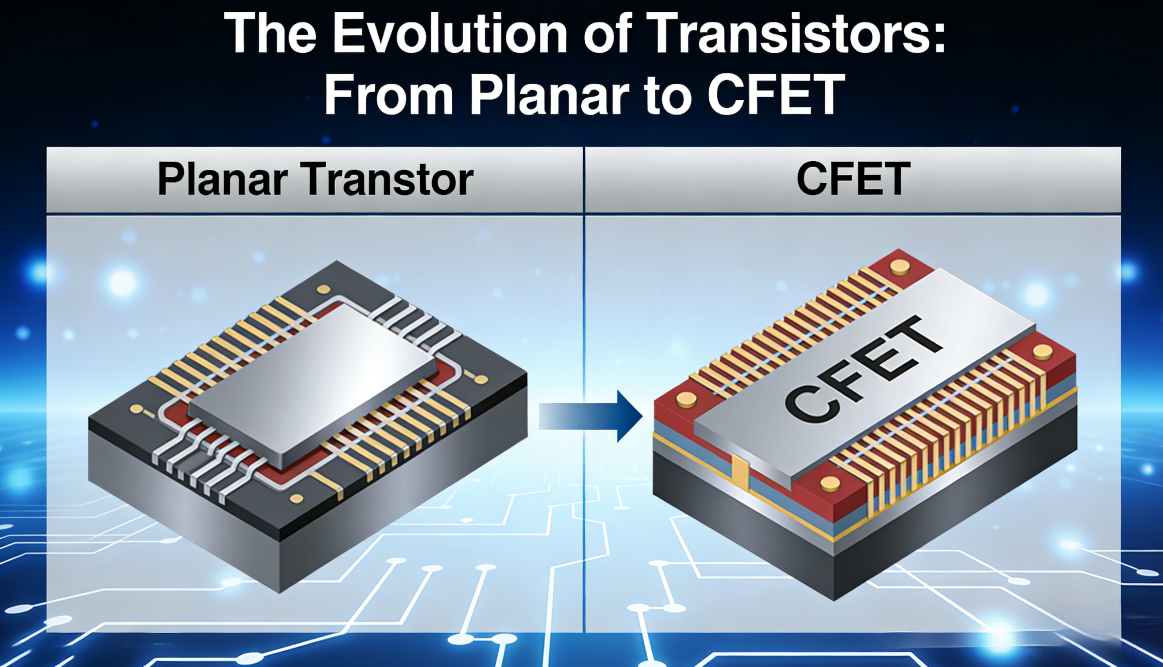

Der Transistor selbst erlebt eine völlige architektonische Revolution.Vom planaren MOSFET zum FinFET, vom GAA-Nanoblech zum CFET-Stacking stellt jeder Schritt einen Übergang vom Schrumpfen zum hin dar Wiederaufbau des Transistors in drei Dimensionen.Dabei handelt es sich nicht nur um eine schrittweise Verbesserung, sondern um eine völlige Neudefinition der Art und Weise, wie Chips Leistung erbringen.

Die vier Generationen der Transistorarchitektur

1. Planarer Transistor (traditionell 2D)

Die klassische flache Struktur, bei der das Tor den Kanal von oben steuert.Es dominierte von den Anfängen bis hinunter zu 40 und 28 nm.Als die Abmessungen weiter schrumpften, wurden Leckstrom und elektrostatische Kontrolle zu unlösbaren Problemen.

2. FinFET (3D-Gate-Steuerung)

Der Kanal wird zu einer vertikalen „Flosse“, wobei sich das Tor um drei Seiten erstreckt.Dies verbessert die elektrostatische Kontrolle drastisch, reduziert Leckagen und ermöglicht eine Skalierung auf 7 nm, 5 nm und sogar 3 nm.FinFET wurde zur Grundlage der modernen Hochleistungschip-Ära.

3. GAA-Nanoblech (Gate-All-Around)

Bei 2 nm und darunter stößt FinFET an seine Grenzen.GAA ersetzt die Finne durch gestapelte horizontale Nanodrähte oder -blätter, die vollständig vom Gate umgeben sind.Es bietet eine bessere Kontrolle, geringere Leistung und einen höheren Antriebsstrom.GAA ist heute die Mainstream-Struktur für Chips der 2-nm-Klasse bei TSMC, Samsung und Intel.

4. CFET (Komplementärer FET)

Die nächste Grenze: NMOS und PMOS vertikal stapeln.CFET bringt zwei Transistoren auf die Grundfläche eines einzigen, wodurch die Fläche drastisch reduziert und die Dichte verbessert wird.Es ist das ultimative evolutionäre Ende der Transistorskalierung, bevor die echte 3D-Systemintegration Einzug hält.

Warum Skalierung allein nicht mehr funktioniert

- Die Prozesskosten steigen mit jedem neuen Knoten exponentiell an

- Quantenleckage und physikalische Einschränkungen verschärfen die Grenzen

- Verbindungsverzögerung und Stromverbrauch übersteigen die Transistorgeschwindigkeit

- Große monolithische Chips leiden unter geringer Ausbeute und hohen Kosten

Die Industrie hat erkannt: Leistung kommt nicht mehr von kleineren Transistoren.Es kommt von bessere Verbindungen, intelligentere Architektur und vertikale Integration.

Die neue Ära: Drei Ebenen der 3D-Innovation

Der Fortschritt in der Halbleiterindustrie wird heute durch drei Dimensionen des 3D-Designs definiert:

- 3D-Transistor: FinFET, GAA, CFET – Aufbau des Transistors vertikal

- 3D-Gerätestapelung: Speicher auf Logik, Hybrid-Bonding, SRAM-Stacking

- 3D-Systemintegration: Chiplet, 2,5D/3D-Gehäuse, Interposer-basierte Integration

Zusammen bilden sie die 3D×3D×3D Ära: Der Transistor, das Gerät und das System werden alle dreidimensional.

DTCO: Die neue Kernkompetenz

Wenn die Skalierung endet, Design-Technologie-Kooptimierung (DTCO) wird kritisch.Es bedeutet, Architektur, Transistorstruktur, Metallführung und Verpackung von Anfang an mitzugestalten.Die stärksten Unternehmen sind nicht mehr nur Prozessführer – sie sind Integratoren auf Systemebene.

Verdrahtungseffizienz, Stromversorgung, thermisches Design und Bandbreitendichte bestimmen nun die tatsächliche Produktleistung.

KI ist die ultimative treibende Kraft

KI und Hochleistungsrechnen erfordern eine beispiellose Bandbreite, Energieeffizienz und Dichte.Diese Anforderungen können durch herkömmliche Skalierung nicht erfüllt werden.Sie erfordern:

- Speicher-Rechenverbindung mit extrem hoher Bandbreite

- Extreme Energieeffizienz pro Vorgang

- Massive Parallelität und dichte Integration

KI hat die gesamte Branche gezwungen, die reine Skalierung aufzugeben und sich einer vollständigen heterogenen 3D-Integration zuzuwenden.

Fazit: Die Zukunft ist nicht kleiner, sie ist höher

Das Zeitalter schrumpfender Transistoren geht zu Ende.Bei der Zukunft der Halbleiter geht es nicht darum, Geräte kleiner zu machen, sondern darum, Systeme aufzubauen höher, dichter und intelligenter vernetzt.

Von Planar über FinFET und GAA bis hin zu CFET hat der Transistor seine Entwicklung abgeschlossen.Die nächste Schlacht wird ausgetragen 3D-Integration, fortschrittliche Verpackung und Design auf Systemebene.Hier wird sich das nächste Jahrzehnt der Halbleiterführerschaft entscheiden.